# **High-Aspect-Ratio Copper-Via-Filling for Three-Dimensional Chip Stacking**

## **II. Reduced Electrodeposition Process Time**

Kazuo Kondo, <sup>a,\*,z</sup> Toshihiro Yonezawa, <sup>b</sup> Daisuke Mikami, <sup>b</sup> Toshikazu Okubo, <sup>c,\*</sup> Yuichi Taguchi, <sup>d</sup> Kenji Takahashi, <sup>d</sup> and Dale P. Barkey <sup>e,\*</sup>

<sup>a</sup>Department of Chemical Engineering, Osaka Prefecture University, 1-1, Gakuen-chyo, Sakai, Osaka, 599-8531, Japan

<sup>b</sup>Department of Applied Chemistry, Okayama University, 3-1-1 Tushimanaka, Okayama 700-0082, Japan

<sup>c</sup>Toppan Printing Company, Limited, Semiconductor Packaging Laboratory, 4-2-3,

Takanodai-minami, Sugito-Cho, Kita-Katsushika-gun, Saitama 354-8508, Japan

<sup>d</sup>Association of Super Advanced Electronic Technologies, Tsukuba Center Incorporated, 1-6, Sengen 2chome, Tsukuba, İbaraki 305-0047, Japan

<sup>e</sup>Department of Chemical Engineering, University of New Hampshire, Durham, New Hampshire 03824, USA

Through-chip electrodes for three-dimensional packaging can offer short interconnection and reduced signal delay. Formation of suitable vias by electrodeposition into cavities presents a filling problem similar to that encountered in the damascene process. Because via dimensions for through-chip filling are larger and have a higher aspect ratio relative to features in damascene, process optimization requires modification of existing superconformal plating baths and plating parameters. In this study, copper filling of high-aspect-ratio through-chip vias was investigated and optimized with respect to plating bath composition and applied current wavetrain. Void-free vias 70  $\mu$ m deep and 10  $\mu$ m wide were formed in 60 min using additives in combination with pulse-reverse current and dissolved-oxygen enrichment. The effects of reverse current and dissolved oxygen on the performance of superfilling additives is discussed in terms of their effects on formation, destruction, and distribution of a Cu(I) thiolate accelerant. © 2005 The Electrochemical Society. [DOI: 10.1149/1.2041047] All rights reserved.

Manuscript submitted February 10, 2005; revised manuscript received June 10, 2005. Available electronically September 8, 2005.

Three-dimensional (3D) chip stacking realizes high-density packaging and high-speed performance. High-aspect-ratio through-chip vias allow short interconnects and reduced signal delays. <sup>1-3</sup> Copper has been selected as the through-chip electrode because of its compatibility with conventional multilayer interconnection in large-scale integration (LSI) and back-end processes.

A typical 3D packaging process proposed by ASET (Association of Super Advanced Electronics Technologies, Japan) includes the following steps: (1) formation of vias 70  $\mu m$  deep by reactive ion etching (RIE); (2) formation of a SiO $_2$  insulating layer; (3) deposition of a TiN barrier layer and a copper seed layer; (4) electrodeposition of copper inside the via; (5) formation of bumps followed by chemical mechanical polishing (CMP), polishing, and dicing of the wafer; and (6) multilayer stacking of chips connected through the copper vias.  $^{1-3}$  The via width is 10  $\mu m$ , and the interconnection pitch is 20  $\mu m$ . The minimum wafer thickness is 50  $\mu m$ , and a 20  $\mu m$  margin is required for polishing the wafer. Hence, a 70  $\mu m$  depth is required for the through-chip electrode, and the via aspect ratio is 7.

Copper electrodeposition in high-aspect-ratio vias is one of the key technologies for 3D packaging. Voids or seams formed in the via may cause serious problems in reliability. An ASET Electronics SI Report published in 2000 (Ref. 4) cited results of via filling with 10  $\mu$ m width and 70  $\mu$ m depth. There were voids and seams in the via center. Sasaki et al. reported fabrication and electronic characterization of 3D chip-stacking technologies with through-chip vias 56  $\mu$ m deep and 13  $\mu$ m in diameter (aspect ratio 4.3). Unfortunately, the details of the electrodeposition process were not reported. In a previous study, we succeeded in filling 70  $\mu$ m vias by optimizing the additive composition and applying pulse-reverse current with an applied current density of  $I_{\rm on} = 2.0$  mA/cm<sup>2</sup>. The solution was made up of 130 g/L CuSO<sub>4</sub>·5H<sub>2</sub>O, 200 g/L H<sub>2</sub>SO<sub>4</sub>, 600 ppm polyethylene glycol (PEG), 100 ppm HCl, 5 ppm bis(3-sulfopropyl)

disulfide (SPS), and increasing Janus Green B (JGB) concentration up to 20 to 50 mg/L. However, void and seam-free filling required 3.5 h.

In the 3D packaging process proposed by ASET, RIE and TiN barrier layer formation and copper seed layer formation require about 10 min. With a high-speed slurry, the CMP time can also be reduced to about 10 min. ASET simulated the process cost of their 3D packaging. If 3.5 h were required to fill the via, copper electrodeposition would be the rate determining step by a substantial margin, and so reduction of the electrodeposition time is required. The objective of this study was to reduce the electrodeposition time to 1 h to make this step compatible with the other operations.

## Experimental

The chip pattern was reported previously.  $^{6-10}$  A chip with high-aspect ratio vias (70 m depth and 10 m width) was fabricated by a two-stage lithography and etching process, with the overhang removed in the second stage. The chip was then mounted on a rotating disk electrode (RDE) and immersed in the copper plating bath. The RDE rotation speed (RDE.; Nikko Keisoku, motor speed controller, SC-5) was fixed at 1000 rpm, and a pulse-reverse current wavetrain (Power Supply HB-211 and BR-101B, Hokoto Denko) was applied. The pulse-reverse wavetrain is defined by three current values, a forward current  $I_{\rm on}$ , a reverse current  $I_{\rm rev}$ , and the off-time current  $I_{\rm off} = 0$ , and by the corresponding time periods  $t_{\rm on}$ ,  $t_{\rm rev}$ , and  $t_{\rm off}$ .

After deposition, cross sections were cut and carefully polished to expose the via centers. The chip was first embedded in resin and cut with a step cutter (MC-170, Marto) to within about 100  $\mu$ m before the via center. The remaining 100  $\mu$ m was then removed by hand polishing, carefully guided by optical microscopy. The cross sections were then examined by field-emission scanning electron microscopy (FESEM) (model S-4300, Hitachi).

Table I shows the plating-bath composition and pulse-reverse plating conditions. The basic bath consisted of 200 g/L  $CuSO_4$   $SH_2O$ , and 100 g/L  $H_2SO_4$ . The additives included a proprietary suppressor (SPR) (0.5, 2, 5, or 10 mg/L) and leveler (LEV) (0, 0.2, or 0.5 mg/L) from EEJA (Electroplating Engineer of Japan), as well as SPS (1, 2, or 10 mg/L) and HCl (50, 70, or 150 mg/L). In a series of experiments at increasing forward current density, begin-

<sup>\*</sup> Electrochemical Society Active Member.

<sup>&</sup>lt;sup>z</sup> E-mail: kkondo@chemeng.osakafu-u.ac.jp

$CuSO_4 \cdot 5H_2O$  $H_2SO_4$

Table I. Plating-bath composition and pulse-reverse current parameters.

Basic bath composition

| 200 g/L<br>25, 50, 75, 100 g/L |

|--------------------------------|

|                                |

$\begin{array}{lll} {\rm SPR} & 0.5, \ 2, \ 5, \ 10 \ {\rm mg/L} \\ {\rm LEV} & 0, \ 0.2, \ 0.5 \ {\rm mg/L} \\ {\rm HCl} & 50, \ 70, \ 150 \ {\rm mg/L} \\ {\rm SPS} \ [{\rm bis}(3{\text{-sulfopropyl}}) \ {\rm disulfide}] & 1, \ 2, \ 10 \ {\rm mg/L} \\ & {\rm Pulse-reverse} \ {\rm conditions} \end{array}$

Pulse-reverse period  $T_{\rm on} = 100, 200, 300 \ {\rm ms}$  Reverse current  $I_{\rm rev}/I_{\rm on} = 1.0, 2.0, 3.0$  Off time  $I_{\rm rev}/I_{\rm on} = 1.0, 2.0, 3.0$

ning with  $I_{\rm on}=4~{\rm mA/cm^2}$ , the additive compositions and plating conditions were optimized. In the optimization procedure, one variable was adjusted at a given applied current until void-free filling was obtained. The current density was then stepped to a higher value, and a second variable was adjusted until void-free filling was obtained. The variables were taken in the order: LEV, SPR, HCL, SPS, and  $\rm H_2SO_4$  concentration, followed by the applied current wavetrain and then sparging with oxygen. In the pulse-reverse experiments, forward deposition times  $T_{\rm on}$  were 100, 200, and 300 ms. Off times  $T_{\rm off}$  were 100, 150, and 200 ms. The ratios  $T_{\rm on}$ : $T_{\rm rev}$ : $T_{\rm off}$  were held equal to 20:1:20. The ratio  $I_{\rm rev}/I_{\rm on}$  was held equal to 1.0, 2.0, or 3.0. In the discussion, parameters  $T_{\rm on}$ : $T_{\rm rev}$ : $T_{\rm off}$  = 200 ms:10 ms:200 ms and  $I_{\rm rev}/I_{\rm on}$  = 2.0 can be assumed unless otherwise specified. Sparging with oxygen was intended to enrich the solution with dissolved oxygen relative to air-saturated solution.

In addition to via-filling experiments, a cyclic voltammetric stripping (CVS) method <sup>11,12</sup> was used to evaluate the inhibition effect of SPR. For these measurements a programmable potentiostat (HZ-3000, Hokoto Denko) and 0.2 cm² platinum RDE were used. The reference electrode was a saturated calomel electrode (SCE). The potential was scanned between 1600 and –500 mV at a rate of 50 mV/s. The copper-stripping charge on the anodic scan was calculated from the area under the voltammogram between 0.0 and 400 mV. A normalized charge was defined by dividing the stripping charge at a given SPR concentration by the charge obtained without SPR.

Time-potential response curves for direct current, pulse, and pulse reverse were obtained on two kinds of electrodes used to simulate the via outside and the via bottom. The via outside was simulated by a copper film electrodeposited on a platinum RDE. This electrode simulates the convective conditions outside of the vias. The via bottom was simulated by a copper electrode patterned with a  $80~\mu m$  thick dry film with  $50{\text -}\mu m{\text -}\text{diameter}$  holes. This electrode simulates a recessed environment that is shielded from convection.

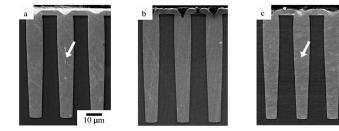

**Figure 1.** Micrographs of via cross sections formed with three different LEV concentrations.  $H_2SO_4$ , SPR, HCl, and SPS concentration is 100~g/L, 0.5~mg/L, 70~mg/L, and 2~mg/L, respectively (a) 0~mg/L LEV; (b) 0.2~mg/L LEV; (c) 0.5~mg/L LEV.

**Figure 2.** Micrographs of via cross sections formed with three different SPR concentrations.  $H_2SO_4$ , LEV, HCl, and SPS concentration is 100 g/L, 0.2 mg/L, 70 mg/L, and 2 mg/L, respectively. (a) 2 mg/L SPR; (b) 5 mg/L SPR; (c) 10 mg/L SPR.

#### **Results and Discussion**

Optimization of leveler concentration.— At forward current densities  $I_{\rm on}$  up to 4 mA/cm², various LEV concentrations were tested in the range of 0.0 to 0.5 mg/L. Typical examples of via cross section micrographs are shown in Fig. 1 for LEV concentrations of 0.0, 0.2, and 0.5 mg/L, with  $I_{\rm on}=4$  mA/cm² and a deposition time of 120 min. At a LEV concentration of 0.0 mg/L, there were large voids at the via center, and at 0.5 mg/L there were small and narrow voids. However, a LEV concentration of 0.2 mg/L produced no voids, and perfect via filling was achieved. With the optimized LEV concentration of 0.2 mg/L and applied current density of  $I_{\rm on}=4$  mA/cm², perfect via filling was achieved in 120 min.

Optimization of suppressor concentration.— The current density was increased to  $I_{\rm on}=5$  mA/cm², and various SPR concentrations in the range of 2.0 to 10.0 mg/L were tested. Typical examples of via cross-section micrographs are shown in Fig. 2 with SPR concentrations of 2.0, 5.0, and 10.0 mg/L for deposition times of 90 min. SPR concentrations of 2.0 and 10.0 mg/L produced small voids at the center, as shown by the arrows. However, a concentration of 5.0 mg/L produced no void, and perfect via filling was achieved. With a SPR concentration of 5.0 mg/L and applied current density of  $I_{\rm on}=5$  mA/cm², perfect via filling was achieved in 90 min.

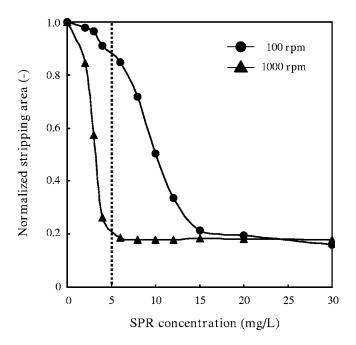

**Figure 3.** Cyclic voltammetric stripping analysis. The normalized integrated stripping charge is plotted against SPR concentration at RDE rotation speeds of 100 and 1000 rpm.

**Figure 4.** Micrographs of via cross sections formed with optimized HCl, SPS and  $\rm H_2SO_4$  concentrations. LEV and SPR concentration is 0.2 and 5 mg/L, respectively. (a) HCl 70 mg/L; (b) SPS 2 mg/L; (c)  $\rm H_2SO_4$  25 mg/L.

Optimization of suppressor concentration by cyclic voltammetric stripping analysis.— Figure 3 shows the normalized CVS stripping area vs SPR concentration. The RDE rotation speed was 100 or 1000 rpm. To simulate the outside of the via, where the fluid velocity is relatively high, a rotation speed of 1000 rpm was used. To simulate the relatively low fluid velocity inside the via, a rotation speed of 100 rpm was used. If the normalized stripping area [area/area (at SPR = 0)] is larger for 100 rpm than for 1000 rpm, deposition is more rapid at the via bottom than the via outside, and bottom-up filling is expected. In Fig. 3, the difference in stripping area between 100 and 1000 rpm is largest at a SPR concentration of 5.0 mg/L. This concentration corresponds to prefect via filling as shown in Fig. 2.

Optimization of HCl, SPS, disulfide, and  $H_2SO_4$  concentrations and pulse-reverse current parameters.— In addition to SPR and LEV, we also optimized the concentrations of HCl, SPS, and  $H_2SO_4$ . HCl was varied from 50 to 150 mg/L,  $H_2SO_4$  from 25 to 100 g/L, and SPS from 1 to 10.0 mg/L. At this stage, we increased the current to  $I_{\rm on}=6$  mA/cm². Typical examples of via cross section micrographs are shown in Fig. 4 with 70 mg/L HCl, 2 mg/L SPS, and 25 g/L  $H_2SO_4$ . Deposition time was 75 min. Even at this optimal composition, small voids were formed at the higher current density.

With  $I_{\rm on}=6~{\rm mA/cm^2},~I_{\rm rev}$  was varied according to  $I_{\rm rev}/I_{\rm on}=1.0,~2.0,~{\rm and}~3.0.$  The resulting via cross sections are shown in Fig. 5 for a deposition time of 75 min. With  $I_{\rm rev}/I_{\rm on}=1.0,~I_{\rm rev}$  is small, the via top was closed, and the deposits had large voids at the center. With  $I_{\rm rev}/I_{\rm on}=2.0,~{\rm the~void~size}$  was smaller. With  $I_{\rm rev}/I_{\rm on}=3.0,~I_{\rm rev}$  is large and large voids were formed at the via bottom.

Oxygen enrichment.— At the optimized additive concentrations and pulse-reverse condition, voids were still produced, and perfect via filling was not obtained at  $I_{\rm on}=6~{\rm mA/cm^2}$  (Fig. 4 and 5). Voidfree filling in 75 min was obtained by enrichment of dissolved  $O_2$  in the solution. We previously reported the via-bottom acceleration effect of dissolved  $O_2$  in through-mask deposition. Hence,  $O_2$  gas

**Figure 5.** Micrographs of via cross sections formed with three different pulse-reverse wavetrains. (a)  $I_{\rm rev}/I_{\rm on}=1.0$ ; (b)  $I_{\rm rev}/I_{\rm on}=2.0$ ; (c)  $I_{\rm rev}/I_{\rm on}=3.0$ .

**Figure 6.** Micrographs of via cross sections formed in the one-stage process with and without  $O_2$  enrichment. (a) without  $O_2$  enrichment; (b) with  $O_2$  enrichment.

was sparged into the plating solution and a pulse-reverse wavetrain with  $I_{\rm on}=6~{\rm mA/cm^2}$  was applied. Figure 6 shows micrographs of via cross sections without and with  $O_2$  sparging. Without  $O_2$  sparging, there is a small void at the via bottom (Fig. 6a; arrow). However, with  $O_2$  sparging there is no void, and perfect via filling is achieved. With  $O_2$  gas sparging, perfect via filling without any voids was achieved at  $I_{\rm on}=6~{\rm mA/cm^2}$  and a deposition time of 75 min, produced no void, and perfect filling was achieved.

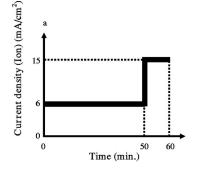

Two-step electrodeposition process.— The filling time was finally reduced to 60 min by application of a two-step deposition process with an initial current density  $I_{\rm on}=6~{\rm mA/cm^2}$  for 50 min and a second higher current density  $I_{\rm on}=15~{\rm mA/cm^2}$  for 10 min with  $O_2$  gas sparging throughout. Figure 7 shows the via cross section obtained by the two-step process; it produced no void and perfect filling was achieved.

Via cross section shapes with 50 min.— The key requirement for perfect via filling is an initial lower current of  $I_{\rm on}=6~{\rm mA/cm^2}$  for 50 min with  $O_2$  gas sparging. Hence, we observed the via cross section with initial lower current of  $I_{\rm on}=6~{\rm mA/cm^2}$  for 50 min without the second step. Figure 8 shows the via cross sections without  $O_2$  and with  $O_2$ . Conformal electrodeposits were formed, and continuous seams from the via bottom to the top remained at the via center without  $O_2$  sparging. However, a clear V shape was formed and perfect via filling was achieved without any seam with  $O_2$  sparging. Formation of this clear V shape leads to perfect via filling. This bottom-up V-shape formation with  $O_2$  is very effective for shortening the electrodeposition time.

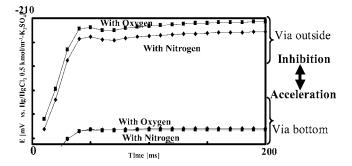

Mechanism of bottom-up filling with oxygen sparging.— Time-potential curves with  $O_2$  and  $N_2$  gas sparging are shown in Fig. 9. The electrodes are the simulated via outside (RDE) and via bottom (through-mask). A pulse-reverse current wavetrain was

**Figure 7.** Time shorting with two-step method. (a) Illustration of current change with two-steps method. (b) Cross-sectional micrographs of via.

**Figure 8.** Micrographs of via cross sections formed in the two-stage process with and without  $O_2$  enrichment. (a) without  $O_2$  enrichment; (b) with  $O_2$  enrichment.

applied. With  $O_2$  gas sparging, the simulated via outside is at a more negative potential, and hence more inhibited than under  $N_2$  sparging. However, no potential difference is observed for the simulated via bottom under  $O_2$  or  $N_2$  sparging.

In equilibrium with the metal, copper plating solutions contain a cuprous ion concentration in the millimolar range. Dissolved oxygen consumes the cuprous ion and removes the solution from equilibrium.  $^{13,14}$  Formation reactions of Cu(I)thiolate accelerator and oxidation reaction of Cu $^{++}$  are shown below  $^{15}$

$$2Cu^{2+} + 4MPS \rightarrow 2Cu()$$

thiolate + SPS + 4H<sup>+</sup> [1]

$$2Cu^{+} + 1/2 O_2 + 2H^{+} \rightarrow 2Cu^{2+} + H_2O$$

[2]

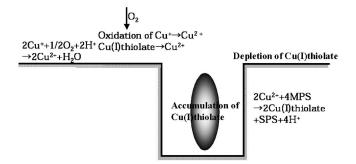

The distribution of these reactions in and around the via is illustrated in Fig. 10. The outside of the via is more accessible to dissolved oxygen than the via bottom, since the chip is rotated at 1000 rpm. The Cu(I)thiolate accelerant is thus readily oxidized to  $\text{Cu}^{2+}$  at the via outside (Eq. 2). Deep inside the via, transport of dissolved  $O_2$  is impeded and accumulation of Cu(I)thiolate occurs. Hence, the Cu(I)thiolate is depleted at the via outside relative to the via bottom, and deposition is more inhibited there. Figure 10 illustrates the mechanism of the bottom-up via filling with  $O_2$  sparging. Depletion of Cu(I)thiolate occurs at the via outside and accumulation of Cu(I)thiolate occurs at the via bottom. This inhibition and acceleration by Cu(I)thiolate accumulation results in the marked V-shaped via cross section observed in Fig. 8b.

#### Conclusions

Void-free filling of  $70~\mu m$  deep and  $10~\mu m$  wide vias was achieved by copper deposition with optimized additive concentrations, a pulse-reverse wavetrain, oxygen enrichment, and a two-stage process. Optimized proprietary additive concentrations of

Figure 9. Chronopotentiometric curves taken under  $N_2$  sparging and under  $O_2$  sparging.

**Figure 10.** Mechanism of bottom-up via filling with  $O_2$  enrichment. Cu(I) is generated at the metal surface by proportionation. It is consumed in solution by reaction with oxygen. Outside the via, consumption of Cu(I) is favored by comparatively rapid transport of dissolved oxygen in the convective regime. Inside the via, transport of dissolved  $O_2$  is impeded and accumulation of Cu(I) thiolate occurs. The result is accumulation of Cu(I) thiolate accelerant inside the via and its depletion outside the via.

5 mg/L SPR and 0.2 mg/L LEV produced void-free filling at 5 mA/cm<sup>2</sup> with a filling time of 90 min. The difference in normalized stripping area [Ar/Ar(SPR = 0)] detected by CVS at RDE rotation speeds of 100 and 1000 rpm shows the largest value at the optimum SPR concentration of 5 mg/L. SPS, HCl, and H<sub>2</sub>SO<sub>4</sub> concentrations were optimized at a current density of  $I_{on} = 6 \text{ mA/cm}^2$ . The optimized concentrations are 2 mg/L SPS, 70 mg/L HCl, and 25 g/L H<sub>2</sub>SO<sub>4</sub>. The optimized pulse-reverse conditions were  $T_{\text{on}}$ :  $T_{\text{rev}}$ :  $T_{\text{off}} = 200 \text{ ms}$ : 10 ms: 200 ms and  $I_{\text{rev}}/I_{\text{on}} = 2.0$ . However, at this composition small voids always formed at a current density of  $I_{\rm on}$  = 6 mA/cm<sup>2</sup>. Perfect via filling was obtained with the optimized plating bath with  $I_{on} = 6 \text{ mA/cm}^2$  and 75 min by sparging with  $O_2$ . The effect of O2 gas is interpreted to result from oxidation of a Cu(I)thiolate accelerant preferentially at the outside of the vias. Finally, a two-step electrodeposition process consisting of initial lower current of  $I_{\text{on}} = 6 \text{ mA/cm}^2$  for 50 min and second higher current of  $I_{on} = 15 \text{ mA/cm}^2 \text{ for } 10 \text{ min was applied, resulting in perfect via}$ filling within 60 min. A clear, bottom-up V-shape-formed via cross section was observed after the initial lower current of  $I_{\rm on} = 6 \text{ mA/cm}^2$ .

### Acknowledgments

This work was supported by NEDO (New Energy Development Organization) as a part of the project of "Research and Development of Ultrahigh-Density Electronics System Integration Technology." Thanks to EEJA Electroplating Engineers of Japan for supplying us with the additives.

Osaka Prefecture University assisted in meeting the publication costs of this article.

#### References

- M. Koyanagi, T. Nakamura, K. W. Lee, Y. Igarashi, T. Mizukusa, Y. Yamada, T. Morooka, and H. Kurino, in *Advanced Metallization Conference 2001 (AMC 2001)*, A. J. McKerrow, Y. Shacham-Diamond, S. Zaima, and T. Ohba, Editors, Conference Proceedings ULSI XVIII, p. 20, The Materials Research Society, Warrendale, PA (2001).

- M. Tomisaka, H. Yonemura, M. Hoshino, and K. Takahashi, in *Solid State Devices and Materials*, p. 40, The Japan Society of Applied Physics, Tokyo (2001).

- K. Takahashi, in The 2nd Annual Meeting on Electronic SI Technologies, p. 43, Tokyo (2001) (in Japanese).

- 4. K. Takahashi, in The 1st Annual Meeting on Electronic SI Technologies, p. 23, Tokyo (2000) (in Japanese).

- T. Harada, K. Asao, K. Sasaki, and Y. Kami, in 2001 ICEP Proceedings, p. 39, Tokyo (2001).

J. Sun, K. Kondo, T. Okamura, S. Oh, M. Tomisaka, H. Vonemura, and M.

- J. Sun, K. Kondo, T. Okamura, S. Oh, M. Tomisaka, H. Yonemura, and M. Hoshino, J. Electrochem. Soc., 150, G355 (2003).

- S. Oh, T. Yonezawa, K. Kondo, M. Tomisaka, H. Yonemura, M. Hoshino, Y. Taguchi, and K. Takahashi, in 2003 ICEP Proceedings, p. 244, Tokyo (2003).

- 8. K. Kondo, T. Okamura, S. Oh, Y. Yonezawa, M. Tomisaka, H. Yonemura, M. Hoshino, Y. Taguchi, and K. Takahashi, *J. Jap. Inst. Electronics Packaging*, **6**, 596

- D. P. Barkey, K. Kondo, T. Matsumoto, and A. Wu, Abstract 189f, AICHE Meeting, San Francisco (2003).

K. Kondo, T. Matsumoto, and K. Watanabe, J. Electrochem. Soc., 151, C250

- D. Tench and C. Ogden, J. Electrochem. Soc., 125, 194 (1978).

P. Taephaisitphonge, Y. Cao, and A. C. West, J. Electrochem. Soc., 148, C492

- P. Taephaistphonge, T. Cao, and A. C. West, J. Electrochem. Soc., 1-10, (2001).

D. P. Barkey, F. Oberholtzer, and Q. Wu, J. Electrochem. Soc., 145, 590 (1998).

D. Hua and D. Barkey, Plat. Surf. Finish., 90, 40 (2003).

E. Farndon, F. C. Walsh, and S. A. Campbell, J. Appl. Electrochem., 25, 572 (2005).